| 芯片设计 | 您所在的位置:网站首页 › are you ready的意思 › 芯片设计 |

芯片设计

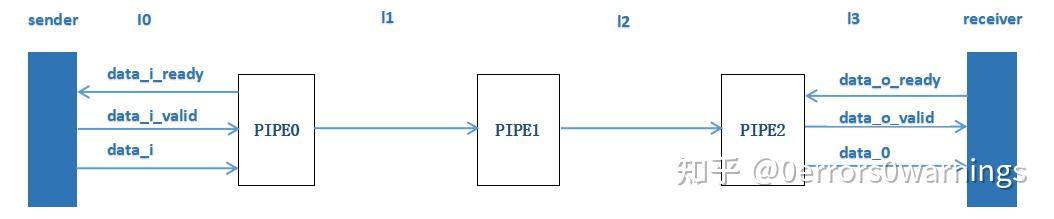

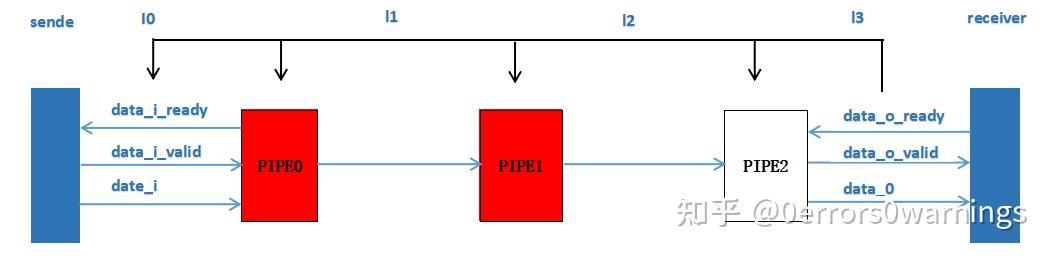

修订记录版本日期说明v0.12022.04.22初版v0.22022.04.27增加对pipe_en的说明v0.32022.05.14增加对skid buffer的说明v0.42022.06.211, pipe_en说明独立成篇https://zhuanlan.zhihu.com/p/531993333?2,skid_buffer说明独立成篇https://zhuanlan.zhihu.com/p/532012806从工厂流水线说起 本来一众打工人在流水线上"快快乐乐"地搬砖,突然receiver处理不过来了,拉低了data_o_ready。为避免数据丢失,得立刻启动应急方案。 应急方案1receiver立刻通知sender,拉低data_i_ready(assign data_i_ready = data_o_ready),不允许再进新数据了。  (注:本章所有图示均用红色表示该pipe处于工作状态,无色表示该pipe处于空闲状态) 此时虽然没有新输入了,但是流水线中的搬砖人没有得到通知,还在继续工作。意味着流水线还会输出3个数据,但是receiver已经拒绝接收数据了。没办法,这时我们得放个fifo在流水线末尾,fifo深度等于流水线级数。  虽然这个方案解决了问题,但增加了fifo,提升了工厂成本。老板不允许,想想其他方案吧。 应急方案2在这个方案中,receiver不仅通知sender暂停,还会通知整个pipe暂停。此时不会有数据输出,也不需要加fifo了。  但从上图我们可以看到,PIPE2是空闲的,这意味着虽然此时receiver拒绝接收,但其实没必要立刻停掉流水线的,完全可以再跑一拍流水的。可能打工人觉得没啥,等一下就好,但工厂老板可不是这样想的。 首先,出现pipe空闲的情况,都是在流水初始阶段,这时候后级流水需要等若干拍才能拿到数据来干活。而我们往往会在完成一次任务后复位流水,而每次复位都会存在PIPE空闲的情况。 我们假设一次任务处理16个数据,流水线为3级,处理完后需要复位流水线。 (注:在ISP中,一般是一帧为一次任务,在vblank期间复位流水线。这里为描述方便简化处理) 理想情况下,需要16+3拍才能完成任务,这里的3拍我们称之为气泡。这意味着对于receiver来说,他需要等待。老板不希望有气泡时间,希望的是他的receiver能够满负荷工作,即一旦receiver准备好了(data_o_ready为高),就能立刻接收到数据。 所以,方案还得改善…… 应急方案3我们得想办法挤掉气泡,别data_o_ready一拉低,大家就摸鱼,可以干的得继续干。 如方案2所提到的,气泡仅出现在流水线初始阶段,且持续拍数=流水级数。也就是说,在前几拍的时候,不用管data_o_ready什么状态,大家努力干活就是。 因此,我们添加一个计数器,当data_i_ready & data_i_valid有效时,计数器+1。当计数器小于流水级数时,流水线保持工作;当计数器≥流水级数时,流水线工作与否取决于data_o_ready.  用代码表示: module pipe_ctrl #( parameter DW = 8 )( input clk, input rst_n, input clear_i, input [7:0] data_num, //data number in a task output data_i_ready, input data_i_valid, input [DW-1:0] data_i, input data_o_ready, output data_o_valid, output [DW-1:0] data_o ); // ------------------- // localparam // ------------------- localparam PIPE_STAGE = 3; // ------------------- // signals def // ------------------- reg [7:0] cnt_i; reg [7:0] cnt_o; wire data_i_end; //data_i finished in this task wire pipe_en; //control the pipe work or pause wire [PIPE_STAGE-1:0] pipe_en_ln; reg [DW-1:0] data0_l1; reg [DW-1:0] data0_l2; reg [DW-1:0] data0_l3; reg [DW-1:0] data1_l1; reg [DW-1:0] data1_l2; reg [DW-1:0] data1_l3; // ------------------- // count // ------------------- always @ (posedge clk or negedge rst_n) begin if(!rst_n) cnt_i |

【本文地址】